Global Wafer Level Packaging Market

Marktgröße in Milliarden USD

CAGR :

%

USD

10.43 Billion

USD

47.92 Billion

2025

2033

USD

10.43 Billion

USD

47.92 Billion

2025

2033

| 2026 –2033 | |

| USD 10.43 Billion | |

| USD 47.92 Billion | |

|

|

|

|

Segmentierung des globalen Marktes für Wafer-Level-Packaging (WLP) nach Integration (Integrated Passive Device, Fan-In-WLP, Fan-Out-WLP und Through-Silicon Via), Technologie (Flip-Chip, Compliant-WLP, konventionelles Chip-Scale-Package, Wafer-Level-Chip-Scale-Package, Nano-Wafer-Level-Packaging und 3D-Wafer-Level-Packaging), Anwendung (Elektronik, IT und Telekommunikation, Industrie, Automobilindustrie, Luft- und Raumfahrt, Gesundheitswesen und Sonstige) sowie Bump-Technologie (Kupfersäule, Lötbumping, Goldbumping und Sonstige) – Branchentrends und Prognose bis 2033

Marktgröße für Wafer-Level-Verpackung

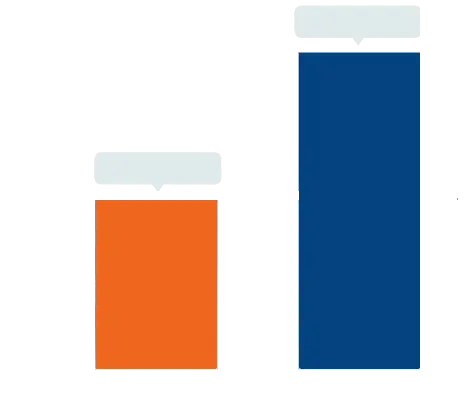

- Der globale Markt für Wafer-Level-Packaging wurde im Jahr 2025 auf 10,43 Milliarden US-Dollar geschätzt und wird voraussichtlich bis 2033 auf 47,92 Milliarden US-Dollar anwachsen , was einer durchschnittlichen jährlichen Wachstumsrate (CAGR) von 21,0 % im Prognosezeitraum entspricht.

- Das Marktwachstum wird maßgeblich durch die steigende Nachfrage nach kompakten, leistungsstarken und energieeffizienten Halbleiterbauelementen in den Bereichen Unterhaltungselektronik, Automobilindustrie und Industrieanwendungen angetrieben. Dies ermutigt Hersteller, fortschrittliche Wafer-Level-Packaging-Verfahren einzusetzen, um die Funktionalität zu verbessern und die Baugröße zu reduzieren.

- Darüber hinaus beschleunigt die steigende Produktion von Smartphones, Wearables und IoT-Geräten den Bedarf an verbesserter Wärmeleistung, höherer Eingangs-/Ausgangsdichte und überlegenen elektrischen Eigenschaften, wodurch die Wafer-Level-Packaging-Technologie zu einer essenziellen Technologie für elektronische Systeme der nächsten Generation wird.

Marktanalyse für Wafer-Level-Packaging

- Die Wafer-Level-Packaging-Technologie, die die Integration mehrerer Funktionen auf Wafer-Ebene ermöglicht, entwickelt sich aufgrund ihrer Fähigkeit, eine höhere Miniaturisierung, verbesserte Zuverlässigkeit und optimierte elektrische Leistung für eine breite Palette von Endgeräten zu erzielen, zu einer Schlüsseltechnologie für die moderne Halbleiterfertigung.

- Die steigende Nachfrage nach Wafer-Level-Packaging wird primär durch die rasanten Fortschritte in der Mobilkommunikation, Sensortechnologien und KI-gestützten Elektronik angetrieben, gepaart mit dem globalen Trend zu kleineren, schnelleren und effizienteren Halbleiterbauteilen, die in den Bereichen Konsumgüter, Automobil und Industrie benötigt werden.

- Der asiatisch-pazifische Raum dominierte 2025 mit einem Anteil von 52,5 % den Markt für Wafer-Level-Packaging. Dies ist auf die starke Präsenz von Halbleiterfertigungszentren, die zunehmende Verbreitung fortschrittlicher Packaging-Technologien in der Unterhaltungselektronik und die expandierenden Produktionsökosysteme in wichtigen Volkswirtschaften zurückzuführen.

- Nordamerika dürfte im Prognosezeitraum die am schnellsten wachsende Region im Markt für Wafer-Level-Packaging sein, bedingt durch die steigende Nachfrage nach Hochleistungshalbleitern in der Unterhaltungselektronik, in Rechenzentren, in der Automobilelektronik und in KI-gesteuerten Geräten.

- Das Segment der integrierten passiven Bauelemente (IPDs) dominierte den Markt bis 2025 mit einem Marktanteil von [Betrag einfügen], bedingt durch die zunehmende Verbreitung in Smartphones, Wearables und HF-Anwendungen, die miniaturisierte Hochleistungskomponenten erfordern. IPDs ermöglichen überlegene elektrische Eigenschaften, reduzierte parasitäre Effekte und eine verbesserte Signalintegrität und sind daher in Hochfrequenz-Kommunikationsgeräten unverzichtbar. Ihre Fähigkeit, mehrere passive Funktionen auf kleinstem Raum zu vereinen, treibt die starke Akzeptanz in der Unterhaltungselektronik und bei drahtlosen Modulen voran. Hersteller bevorzugen IPDs zudem aufgrund ihrer Eignung für die Massenproduktion bei gleichzeitig hoher Kosteneffizienz. Die zunehmende Integration fortschrittlicher Kommunikationsstandards wie 5G steigert die Nachfrage nach IPD-basierten WLP-Lösungen in kompakten Elektronikarchitekturen zusätzlich.

Berichtsumfang und Marktsegmentierung für Wafer-Level-Packaging

|

Attribute |

Wichtige Markteinblicke in die Wafer-Level-Verpackung |

|

Abgedeckte Segmente |

|

|

Abgedeckte Länder |

Nordamerika

Europa

Asien-Pazifik

Naher Osten und Afrika

Südamerika

|

|

Wichtige Marktteilnehmer |

|

|

Marktchancen |

|

|

Mehrwertdaten-Infosets |

Zusätzlich zu den Erkenntnissen über Marktszenarien wie Marktwert, Wachstumsrate, Segmentierung, geografische Abdeckung und Hauptakteure enthalten die von Data Bridge Market Research erstellten Marktberichte auch Import-Export-Analysen, einen Überblick über die Produktionskapazität, eine Analyse des Produktionsverbrauchs, eine Preistrendanalyse, ein Klimawandelszenario, eine Lieferkettenanalyse, eine Wertschöpfungskettenanalyse, einen Überblick über Rohstoffe/Verbrauchsmaterialien, Kriterien für die Lieferantenauswahl, eine PESTLE-Analyse, eine Porter-Analyse und den regulatorischen Rahmen. |

Markttrends für Wafer-Level-Packaging

Zunehmende Verbreitung fortschrittlicher Fan-Out- und 3D-Wafer-Level-Packaging-Technologien

- Der Markt für Wafer-Level-Packaging (WLP) erlebt einen starken Wandel hin zu fortschrittlichen Fan-Out- und 3D-Architekturen, da Hersteller höhere Leistung und größere Integrationsdichte für Halbleiterbauelemente der nächsten Generation priorisieren. Dieser Trend wird durch den steigenden Bedarf an verbesserter elektrischer Leistung, dünneren Bauformen und erhöhter thermischer Effizienz in Anwendungen wie Smartphones, Hochleistungsrechnern und Automobilelektronik geprägt.

- Deca Technologies hat beispielsweise seine Fan-Out-Packaging-Kapazitäten erweitert, um führende Halbleiterhersteller zu unterstützen, die einen höheren Durchsatz und eine verbesserte Designflexibilität für komplexe Chiparchitekturen anstreben. Dies zeigt, wie Branchenakteure Innovationen durch skalierbare Fan-Out-Plattformen beschleunigen.

- Fan-Out und 3D-Wafer-Level-Packaging ermöglichen kürzere Verbindungen, eine höhere I/O-Dichte und eine verbesserte System-in-Package-Integration. Dadurch sind sie unerlässlich für fortschrittliche Prozessoren, KI-Beschleuniger und Edge-Computing-Geräte, die kompakte Designs mit hoher Energieeffizienz erfordern. Dieser Wandel wird zusätzlich durch die Optimierung der Fertigung vorangetrieben, um die Leistung zu steigern und gleichzeitig die Kosten zu kontrollieren.

- Die Nachfrage nach heterogener Integration fördert die Einführung dieser fortschrittlichen WLP-Ansätze, da Chiphersteller mehrere Funktionen wie Speicher-, Logik- und HF-Komponenten in kompakten Gehäusen integrieren. Dieser Trend wird auch durch die Notwendigkeit angetrieben, die Skalierungsgrenzen traditioneller 2D-Architekturen zu überwinden.

- Unternehmen konzentrieren sich auf den Ausbau ihrer Produktionskapazitäten und die Stärkung der Forschung und Entwicklung für Packaging-Technologien der nächsten Generation. Dies beschleunigt die Einführung von Fan-Out- und 3D-Strukturen in verschiedenen mikroelektronischen Anwendungen. Dieser Fokus verändert die Erwartungen an Leistung und Miniaturisierung im Halbleiter-Packaging.

- Der zunehmende Fokus auf höhere Systemfunktionalität bei kleinerem Platzbedarf treibt die Hersteller zu fortschrittlichen Wafer-Level-Packaging-Lösungen und verleiht diesem Trend damit eine starke Dynamik für die weitere Verbreitung in den Bereichen Unterhaltungselektronik, Automobilindustrie und Hochleistungsrechnen.

Marktdynamik der Wafer-Level-Packaging-Technologie

Treiber

Wachsende Nachfrage nach miniaturisierten und leistungsstarken Halbleiterbauelementen

- Die steigende Nachfrage von Verbrauchern und Industrie nach kompakten, energieeffizienten und leistungsstarken Halbleiterbauelementen treibt die Verbreitung von Wafer-Level-Packaging-Lösungen in vielfältigen Anwendungen voran. Da elektronische Geräte immer kleiner und fortschrittlicher werden, bietet WLP die für moderne Chiparchitekturen erforderliche Dichte, Geschwindigkeit und Zuverlässigkeit.

- Amkor Technology erweitert beispielsweise kontinuierlich sein Portfolio an fortschrittlichen Wafer-Level-Packaging-Lösungen, um den wachsenden Bedarf von Smartphone- und Computerherstellern an dünneren Bauformen und höherer Funktionalität zu decken.

- Die Miniaturisierungstrends in der Unterhaltungselektronik, wie z. B. bei Wearables, IoT-Knoten und Smartphones, treiben die Nachfrage nach Gehäuselösungen an, die eine hohe I/O-Dichte, verbesserte Signalintegrität und reduzierte Latenz ermöglichen. WLP (Wide Laser Packet) ermöglicht diese Eigenschaften durch Minimierung der Verbindungslängen und Optimierung der elektrischen Pfade innerhalb des Chipgehäuses.

- Die steigenden Erwartungen an geringen Stromverbrauch und verbesserte Gerätefunktionalität veranlassen Hersteller dazu, Wafer-Level-Packaging als bevorzugte Integrationslösung sowohl für Konsumgüter- als auch für Industrieanwendungen einzusetzen. Dies unterstreicht seine entscheidende Rolle in der Halbleiterentwicklung der nächsten Generation.

- Die steigende Nachfrage nach Hochleistungsrechnern und kompakter Elektronik positioniert WLP weiterhin als essentielle Technologie und schließt diesen Treiber mit seiner Bedeutung für die Miniaturisierung von Chips und Leistungssteigerungen ab.

Zurückhaltung/Herausforderung

Hoher Kapitalbedarf und komplexe Fertigungsanforderungen

- Der Markt für Wafer-Level-Packaging (WLP) steht aufgrund der hohen Investitionen in die moderne Fertigungsinfrastruktur und der komplexen Produktionsprozesse vor großen Herausforderungen. Der Aufbau von WLP-Fertigungslinien erfordert kostspielige Ausrüstung, Präzisionswerkzeuge und spezielle Reinraumumgebungen, was Eintrittsbarrieren für neue Marktteilnehmer und kleinere Unternehmen schafft.

- Unternehmen, die in hochmoderne Lithografie-, Bonding- und Messtechnik investieren, stehen beispielsweise vor erheblichen finanziellen Verpflichtungen, die ihre Fähigkeit zu einer schnellen Kapazitätserweiterung einschränken können. Fortschrittliche WLP-Prozesse wie Fan-Out, 3D-Stapelung und heterogene Integration erfordern umfassendes Fertigungs-Know-how, präzise Ausrichtung und fortschrittliche Materialhandhabungstechniken, was die betriebliche Komplexität erhöht. Diese Anforderungen machen die Prozessoptimierung zu einer großen Herausforderung für viele Halbleiter-Packaging-Werke.

- Der Bedarf an kontinuierlichen Investitionen in Forschung und Entwicklung, Prozessautomatisierung und Qualitätssicherung erhöht den Kostendruck zusätzlich, insbesondere da sich die Verpackungstechnologien weiterentwickeln, um höhere Integrationsgrade und feinere Strukturgrößen zu ermöglichen. Diese Komplexität verlangsamt die Akzeptanz bei kostensensiblen Herstellern.

- Mit fortschreitenden Produktionstechnologien wird die Aufrechterhaltung einer stabilen Ausbeute und Prozesskonsistenz aufgrund zahlreicher Fertigungsschritte und eines höheren Fehlerrisikos zunehmend schwieriger, was zu betrieblichen Herausforderungen führt. Diese Probleme beeinträchtigen Skalierbarkeit und Kosteneffizienz.

- Die Kombination aus hohem Kapitalbedarf und komplexen Fertigungsabläufen stellt weiterhin eine Herausforderung für eine breitere Anwendung dar. Abschließend wird in diesem Abschnitt die Bedeutung der Berücksichtigung von Kosten-, Kapazitäts- und Fertigungskompetenzengpässen bei der WLP-Expansion hervorgehoben.

Marktumfang für Wafer-Level-Packaging

Der Markt ist segmentiert nach Integration, Technologie, Anwendung und Stoßtechnologie.

- Durch Integration

Basierend auf der Integration ist der Markt für Wafer-Level-Packaging (WLP) in Integrated Passive Devices (IPD), Fan-In WLP, Fan-Out WLP und Through-Silicon Via (TSV) unterteilt. Das Segment der integrierten passiven Bauelemente dominierte den Markt im Jahr 2025 aufgrund seiner zunehmenden Verbreitung in Smartphones, Wearables und HF-Anwendungen, die miniaturisierte Hochleistungskomponenten erfordern. IPDs ermöglichen überlegene elektrische Eigenschaften, reduzierte parasitäre Effekte und eine verbesserte Signalintegrität und sind daher in Hochfrequenz-Kommunikationsgeräten unverzichtbar. Ihre Fähigkeit, mehrere passive Funktionen auf kleinem Raum zu vereinen, trägt maßgeblich zur starken Akzeptanz in der Unterhaltungselektronik und bei drahtlosen Modulen bei. Hersteller bevorzugen IPDs auch aufgrund ihrer Eignung für die Massenproduktion bei gleichzeitig hoher Kosteneffizienz. Die zunehmende Integration fortschrittlicher Kommunikationsstandards wie 5G steigert die Nachfrage nach IPD-basierten WLP-Lösungen in kompakten Elektronikarchitekturen zusätzlich.

Das Segment Fan-Out WLP wird voraussichtlich von 2026 bis 2033 das schnellste Wachstum verzeichnen. Grund dafür ist die Eignung dieser Technologie für Anwendungen, die eine hohe I/O-Dichte sowie verbesserte thermische und elektrische Eigenschaften erfordern. Fan-Out WLP ermöglicht die Umverteilung von Verbindungen und damit komplexere Gehäuse bei gleichzeitig geringer Bauhöhe. Dies macht die Technologie in mobilen Prozessoren der nächsten Generation und Power-Management-ICs beliebt. Sie findet zunehmend Anwendung in Fahrerassistenzsystemen (ADAS), kompakter tragbarer Elektronik und IoT-Modulen, die eine effiziente Wärmeableitung und hohe Zuverlässigkeit erfordern. Ihre Skalierbarkeit für die heterogene Integration positioniert sie stark im Bereich der sich entwickelnden Halbleiterdesigns. Kontinuierliche Weiterentwicklungen führender Halbleiterunternehmen zur Erweiterung der Fan-Out-Kapazitäten werden das starke Wachstum im Prognosezeitraum weiter beflügeln.

- Durch Technologie

Basierend auf der Technologie ist der Markt in Flip-Chip, Compliant WLP, Conventional Chip Scale Package, Wafer Level Chip Scale Package (WLCSP), Nano WLP und 3D WLP unterteilt. Das WLCSP-Segment dominierte den Markt im Jahr 2025 aufgrund seiner weitverbreiteten Anwendung in Mobilgeräten, Unterhaltungselektronik und Automobilsensoren, die ultrakompakte Bauformen erfordern. WLCSP bietet Vorteile wie geringe Induktivität, hervorragende thermische Eigenschaften, hohe Zuverlässigkeit und echte Chip-Größen-Gehäuse und ist daher für die Massenfertigung besonders geeignet. Die Technologie unterstützt effiziente elektrische Eigenschaften, die für HF-, Energiemanagement- und MEMS-Bauelemente entscheidend sind. WLCSP reduziert zudem Verarbeitungsschritte und Verpackungskosten und fördert so die Integration großer Stückzahlen durch führende Halbleiterhersteller. Seine Kompatibilität mit fortschrittlichen Fertigungstechnologien sichert die anhaltende Marktführerschaft in der miniaturisierten Elektronik.

Das Segment der 3D-Wafer-Level-Packaging-Technologien (3D-WLP) wird aufgrund des steigenden Bedarfs an fortschrittlichen Stapelarchitekturen, die Leistung und Bandbreite verbessern, voraussichtlich bis 2033 das schnellste Wachstum verzeichnen. Diese Technologie unterstützt die vertikale Integration von Chips und ermöglicht so kürzere Verbindungen und höhere Verarbeitungsgeschwindigkeiten – entscheidend für HPC, KI-Beschleuniger und Speicherbausteine der nächsten Generation. 3D-WLP bietet außergewöhnliche Skalierbarkeit für komplexe Halbleiterdesigns, die höhere Funktionalität auf kleinem Raum erfordern. Die zunehmende Verbreitung der 3D-Integration in Rechenzentren, leistungsstarker Unterhaltungselektronik und Automobilelektronik beschleunigt ihren Einsatz. Kontinuierliche Fortschritte bei Through-Silicon-Via- und Hybrid-Bonding-Technologien stärken die Rolle von 3D-WLP im Ökosystem der Halbleiterverpackung.

- Durch Bewerbung

Basierend auf den Anwendungsbereichen ist der Markt für Wafer-Level-Packaging (WLP) in Elektronik, IT & Telekommunikation, Industrie, Automobilindustrie, Luft- und Raumfahrt, Gesundheitswesen und Sonstige unterteilt. Das Segment Elektronik dominierte den Markt im Jahr 2025, angetrieben durch den massiven Konsum von Smartphones, Wearables, Tablets und AR/VR-Geräten, die kompakte und leistungsstarke Halbleitergehäuse erfordern. Die zunehmende Verbreitung miniaturisierter integrierter Schaltungen und Sensoren in der Unterhaltungselektronik verstärkt die Nachfrage nach WLP zusätzlich. Das Segment profitiert erheblich vom Bedarf an energieeffizienten, thermisch effizienten und kostengünstigen Chips in tragbaren Elektronikgeräten. WLP-Technologien ermöglichen erweiterte Funktionalität auf begrenztem Platinenraum und unterstützen Hersteller bei der Entwicklung schlankerer und leistungsstärkerer Geräte. Kontinuierliche Innovationen bei Konsumgeräten weltweit sichern dem Segment Elektronik seine führende Position.

Im Automobilsegment wird aufgrund des steigenden Elektronikanteils in modernen Fahrzeugen, darunter Fahrerassistenzsysteme (ADAS), Infotainmentsysteme, Leistungselektronik und Elektrofahrzeugplattformen, von 2026 bis 2033 das schnellste Wachstum erwartet. Anwendungen im Automobilbereich erfordern hochzuverlässige und robuste Gehäuselösungen, die extremen Temperaturen und Vibrationen standhalten – WLP ist daher eine attraktive Option. Die Umstellung auf Fahrzeugelektrifizierung und autonomes Fahren erfordert fortschrittliche Halbleiterkomponenten mit überlegener Effizienz und Verarbeitungsleistung. WLP unterstützt die kompakte Integration von Sensoren, Mikrocontrollern und Power-Management-ICs, die für die Automobilarchitekturen der nächsten Generation unerlässlich sind. Steigende Investitionen von Automobilherstellern und Tier-1-Zulieferern in fortschrittliche Halbleitertechnologien beschleunigen das Wachstum des Segments zusätzlich.

- Durch die Nutzung von Technologie

Basierend auf der verwendeten Löttechnologie ist der Markt in Kupfersäulen-, Lötbump-, Goldbump- und sonstige Verfahren unterteilt. Das Segment der Lötbumps dominierte den Markt im Jahr 2025 aufgrund seiner Marktreife, Kosteneffizienz und breiten Anwendung in einer Vielzahl von Halbleiterbauelementen. Lötbumps gewährleisten zuverlässige elektrische und mechanische Verbindungen für Flip-Chip- und Wafer-Level-Packaging und eignen sich daher ideal für die Massenfertigung. Das Verfahren zeichnet sich durch gute thermische Eigenschaften und Kompatibilität mit verschiedenen Anwendungen aus, darunter Mobilprozessoren, Speicher und HF-Komponenten. Die langjährige, etablierte Lieferkette und Fertigungsinfrastruktur festigen die führende Marktposition zusätzlich. Die Technologie bleibt die bevorzugte Wahl für ein optimales Verhältnis von Leistung, Kosten und Fertigungseffizienz in der Halbleiterproduktion.

Das Segment der Kupfersäulen-Technologie wird im Prognosezeitraum voraussichtlich das schnellste Wachstum verzeichnen. Dies ist auf die überlegene Stromtragfähigkeit, die verbesserte Wärmeableitung und die Möglichkeit zur Feinstrukturierung zurückzuführen. Kupfersäulen-Bumping wird zunehmend in hochdichten und leistungsstarken Geräten wie fortschrittlichen Logikchips, KI-Prozessoren und Speichern mit hoher Bandbreite eingesetzt. Die Technologie ermöglicht dünnere Verbindungen und eine bessere Elektromigrationsbeständigkeit und eignet sich daher für moderne, kompakte Halbleiterarchitekturen. Mit der zunehmenden Verbreitung fortschrittlicher Packaging-Verfahren wie 2,5D- und 3D-Integration gewinnt Kupfersäulen-Bumping weiter an Bedeutung. Die steigende Akzeptanz in der Automobilelektronik, in Rechenzentren und in der Premium-Unterhaltungselektronik beschleunigt das Wachstum bis 2033.

Regionale Analyse des Marktes für Wafer-Level-Packaging

- Der asiatisch-pazifische Raum dominierte 2025 mit einem Umsatzanteil von 52,5 % den Markt für Wafer-Level-Packaging. Treiber dieser Entwicklung waren die starke Präsenz von Halbleiterfertigungszentren, die zunehmende Verbreitung fortschrittlicher Packaging-Technologien in der Unterhaltungselektronik sowie die expandierenden Produktionsökosysteme in wichtigen Volkswirtschaften.

- Die kosteneffizienten Produktionskapazitäten der Region, die zunehmenden Investitionen in Wafer-Level-Technologien und das rasante Wachstum in der Herstellung von Hardware für mobile Geräte und das Internet der Dinge beschleunigen die gesamte Marktexpansion.

- Die Verfügbarkeit qualifizierter Ingenieure, förderliche staatliche Initiativen zur Halbleiterentwicklung und der hohe Elektronikkonsum in Schwellenländern tragen maßgeblich zur Verbreitung des Wafer-Level-Packaging bei.

Einblick in den chinesischen Markt für Wafer-Level-Verpackungen

China wird 2025 den größten Anteil am asiatisch-pazifischen Markt für Wafer-Level-Packaging halten, was auf seine dominante Stellung in der Halbleitermontage, -prüfung und der Produktion von Unterhaltungselektronik zurückzuführen ist. Die wachsenden Foundry-Kapazitäten des Landes, die starke staatliche Unterstützung durch Programme zur Förderung der Halbleiter-Selbstversorgung und der zunehmende Fokus auf fortschrittliche Packaging-Technologien sind die wichtigsten Wachstumstreiber. Die Nachfrage wird zusätzlich durch die Massenproduktion von Smartphones, Wearables und Hochleistungsprozessoren für den Inlands- und Weltmarkt gestützt.

Einblick in den indischen Markt für Wafer-Level-Packaging

Indien verzeichnet das schnellste Wachstum im asiatisch-pazifischen Raum. Treiber dieser Entwicklung sind steigende Investitionen in Halbleiterfertigungs- und Testanlagen, die wachsende Nachfrage nach fortschrittlichen Gehäusetechnologien für Smartphones und Automobilelektronik sowie staatliche Förderprogramme für die Halbleiterproduktion. Die Initiative „Make in India“ und das zunehmende Interesse globaler Chiphersteller fördern die Verbreitung von Wafer-Level-Packaging. Der Ausbau der heimischen Elektronikfertigung und das rasante Wachstum des Konsums von Endgeräten tragen zusätzlich zur starken Marktdynamik bei.

Einblick in den europäischen Markt für Wafer-Level-Packaging

Der europäische Markt für Wafer-Level-Packaging wächst stetig, angetrieben durch die starke Nachfrage nach fortschrittlichen Halbleiterlösungen in der Automobilelektronik, der industriellen Automatisierung und in Anwendungen mit hohen Zuverlässigkeitsanforderungen. Die Region legt Wert auf qualitativ hochwertige Fertigung, strenge regulatorische Standards und technologischen Fortschritt in der Hochleistungsmikroelektronik. Die zunehmende Verbreitung miniaturisierter Bauelemente, laufende Investitionen in Forschung und Entwicklung sowie der steigende Bedarf an effizienten Gehäusen für Sensoren und Leistungselektronik fördern das Marktwachstum zusätzlich.

Einblick in den deutschen Markt für Wafer-Level-Packaging

Der deutsche Markt für Wafer-Level-Packaging wird durch seine führende Rolle in der Automobilelektronik, im Maschinenbau und in der Präzisions-Halbleiterfertigung angetrieben. Wesentliche Faktoren hierfür sind die starke Forschungs- und Entwicklungsinfrastruktur des Landes, die Kooperationen zwischen akademischen Forschungseinrichtungen und Halbleiterunternehmen sowie die Nachfrage nach hochzuverlässigen Komponenten in Automobil- und Industrieanwendungen. Die zunehmende Integration von Sensoren, Leistungshalbleitern und Mikrocontrollern in Fahrzeugen der nächsten Generation fördert die Verbreitung fortschrittlicher Packaging-Technologien.

Einblick in den britischen Markt für Wafer-Level-Packaging

Der britische Markt profitiert von einem ausgereiften Ökosystem für Elektronikdesign, kontinuierlichen Bemühungen zur Stärkung der Resilienz der Halbleiterlieferkette und steigenden Investitionen in die Spitzenforschung für Mikroelektronik und Nanofabrikation. Die enge Zusammenarbeit zwischen Wissenschaft und Industrie, das Wachstum bei Innovationen in der Medizinelektronik und der Fokus auf die Entwicklung hochwertiger Halbleiter festigen weiterhin die Rolle Großbritanniens im Bereich spezialisierter Gehäusetechnologien. Besonders stark ist die Nachfrage nach Instrumenten für die Biowissenschaften, Kommunikationsgeräten und industriellen Systemen.

Einblick in den nordamerikanischen Markt für Wafer-Level-Packaging

Nordamerika wird voraussichtlich von 2026 bis 2033 das schnellste jährliche Wachstum verzeichnen. Treiber dieser Entwicklung ist die steigende Nachfrage nach Hochleistungshalbleitern in den Bereichen Unterhaltungselektronik, Rechenzentren, Automobilelektronik und KI-gestützte Geräte. Die Region profitiert von modernsten Forschungs- und Entwicklungskapazitäten, der starken Präsenz führender fabless Halbleiterunternehmen und der raschen Einführung von 3D- und fortschrittlichen Wafer-Packaging-Technologien. Die zunehmende Rückverlagerung der Halbleiterfertigung und erhebliche staatliche Investitionen in die Chipherstellung beschleunigen das Marktwachstum zusätzlich.

Einblick in den US-amerikanischen Markt für Wafer-Level-Packaging

Die USA werden 2025 den größten Anteil am nordamerikanischen Markt für Wafer-Level-Packaging (WLP) halten. Dies ist auf ihr starkes Innovationsökosystem im Halbleiterbereich, fortschrittliche Forschungs- und Entwicklungsprogramme im Bereich Packaging sowie ihre bedeutenden Produktionskapazitäten für Hochleistungsrechner, Kommunikationsgeräte und Automobilelektronik zurückzuführen. Der Fokus des Landes auf Technologieführerschaft, hohe Investitionen in Chipdesign und die Präsenz großer Halbleiterhersteller und -gießereien tragen zu einer starken Nachfrage nach WLP bei. Die zunehmende Integration von KI, Cloud Computing und Elektronik für Elektrofahrzeuge stärkt die Position der USA auf dem regionalen Markt zusätzlich.

Marktanteil der Wafer-Level-Verpackung

Die Wafer-Level-Packaging-Industrie wird hauptsächlich von etablierten Unternehmen dominiert, darunter:

- JCET Group Co., Ltd. (China)

- NEMOTEK Technologie (Marokko)

- Chipbond Technology Corporation (Taiwan)

- Fujitsu (Japan)

- Powertech Technology Inc. (Taiwan)

- China Wafer Level CSP Co., Ltd. (China)

- Siliconware Precision Industries Co., Ltd. (Taiwan)

- Amkor Technology (USA)

- IQE PLC (UK)

- ChipMOS Technologies Inc. (Taiwan)

- Deca Technologies (USA)

- Qualcomm Technologies, Inc. (USA)

- Toshiba Corporation (Japan)

- Tokyo Electron Limited (Japan)

- Applied Materials, Inc. (USA)

- Lam Research Corporation (USA)

- ASML (Niederlande)

- Infineon Technologies AG (Deutschland)

- KLA Corporation (USA)

- Marvell (USA)

Neueste Entwicklungen auf dem globalen Markt für Wafer-Level-Packaging

- Im September 2024 kündigte Samsung Electronics eine bedeutende Erweiterung seines Ökosystems für fortschrittliche Gehäuselösungen an. Dazu integriert das Unternehmen verbesserte Wafer-Level-Packaging- und Chiplet-Montagekapazitäten in seine Produktionsstätten in Südkorea. Diese Initiative stärkt die Position des Unternehmens im Bereich der heterogenen Integration, unterstützt die steigende Nachfrage nach hochdichten Halbleitergehäusen für KI- und HPC-Anwendungen und beschleunigt die Einführung von WLP-Technologien der nächsten Generation durch höhere Produktionseffizienz und kürzere Entwicklungszyklen.

- Im August 2024 gab ASE Technology Holding Pläne zur Modernisierung ihrer Produktionsstätten in Taiwan bekannt. Geplant sind Wafer-Level-Testplattformen der nächsten Generation und fortschrittliche Automatisierungssysteme. Diese Investition erhöht die Produktionsstabilität, ermöglicht die Fertigung größerer Stückzahlen kompakter und zuverlässiger WLP-Lösungen und stärkt die Fähigkeit des Unternehmens, die steigende Nachfrage aus den Bereichen Automobilelektronik, IoT-Geräte und fortschrittliche Konsumgüteranwendungen zu decken.

- Im März 2024 schlossen die Arizona State University und Deca Technologies eine Partnerschaft, um Nordamerikas erstes spezialisiertes Forschungs- und Entwicklungszentrum für Fan-Out-Wafer-Level-Packaging (FOWLP) zu gründen. Diese Zusammenarbeit stärkt die technologische Führungsrolle der USA im Bereich Advanced Packaging, beschleunigt Innovationen bei FOWLP-Architekturen und unterstützt die Resilienz der heimischen Halbleiter-Lieferkette durch die Förderung der gemeinsamen Entwicklung von Prozessen der nächsten Generation durch Industrie und Wissenschaft.

- Im März 2024 kündigte die Taiwan Semiconductor Manufacturing Company Limited (TSMC) im Rahmen ihrer globalen Expansionsstrategie den Ausbau ihrer Kapazitäten für fortschrittliche Chip-Packaging-Technologien in Japan an. Diese Erweiterung verbessert die regionale Fertigungskompetenz, stärkt die Diversifizierung der Lieferkette und unterstützt die wachsende Nachfrage nach Wafer-Level-Packaging-Technologien für Hochleistungsgeräte und fortschrittliche Logikanwendungen.

- Im Juni 2023 eröffnete Onto Innovation an seinem Hauptsitz in Wilmington, Massachusetts, sein Kompetenzzentrum für Anwendungen im Bereich Panel-Level-Packaging (PLP). Diese Einrichtung bietet Kunden direkten Zugriff auf Ausrüstung, Software und kollaborative Prozessumgebungen, die Technologie-Roadmaps beschleunigen, die PLP- und WLP-Prozessoptimierung verbessern und die Markteinführungszeit für fortschrittliche Halbleiter-Packaging-Lösungen verkürzen.

SKU-

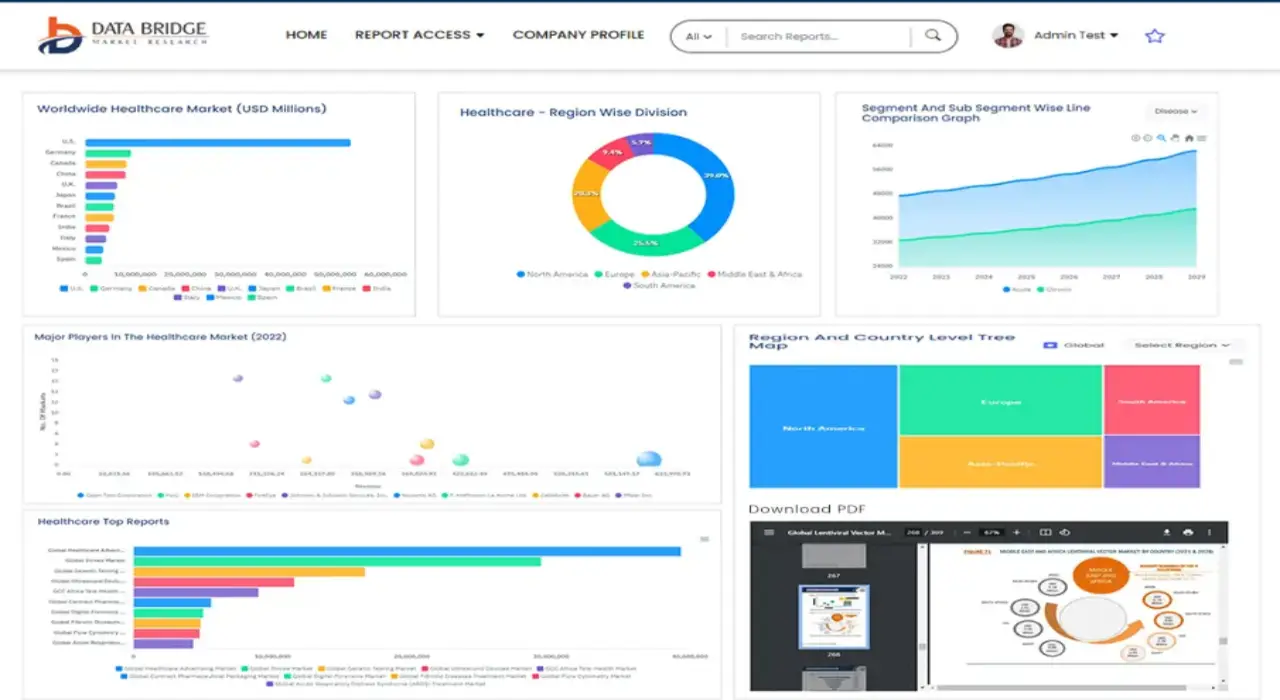

Erhalten Sie Online-Zugriff auf den Bericht zur weltweit ersten Market Intelligence Cloud

- Interaktives Datenanalyse-Dashboard

- Unternehmensanalyse-Dashboard für Chancen mit hohem Wachstumspotenzial

- Zugriff für Research-Analysten für Anpassungen und Abfragen

- Konkurrenzanalyse mit interaktivem Dashboard

- Aktuelle Nachrichten, Updates und Trendanalyse

- Nutzen Sie die Leistungsfähigkeit der Benchmark-Analyse für eine umfassende Konkurrenzverfolgung

Forschungsmethodik

Die Datenerfassung und Basisjahresanalyse werden mithilfe von Datenerfassungsmodulen mit großen Stichprobengrößen durchgeführt. Die Phase umfasst das Erhalten von Marktinformationen oder verwandten Daten aus verschiedenen Quellen und Strategien. Sie umfasst die Prüfung und Planung aller aus der Vergangenheit im Voraus erfassten Daten. Sie umfasst auch die Prüfung von Informationsinkonsistenzen, die in verschiedenen Informationsquellen auftreten. Die Marktdaten werden mithilfe von marktstatistischen und kohärenten Modellen analysiert und geschätzt. Darüber hinaus sind Marktanteilsanalyse und Schlüsseltrendanalyse die wichtigsten Erfolgsfaktoren im Marktbericht. Um mehr zu erfahren, fordern Sie bitte einen Analystenanruf an oder geben Sie Ihre Anfrage ein.

Die wichtigste Forschungsmethodik, die vom DBMR-Forschungsteam verwendet wird, ist die Datentriangulation, die Data Mining, die Analyse der Auswirkungen von Datenvariablen auf den Markt und die primäre (Branchenexperten-)Validierung umfasst. Zu den Datenmodellen gehören ein Lieferantenpositionierungsraster, eine Marktzeitlinienanalyse, ein Marktüberblick und -leitfaden, ein Firmenpositionierungsraster, eine Patentanalyse, eine Preisanalyse, eine Firmenmarktanteilsanalyse, Messstandards, eine globale versus eine regionale und Lieferantenanteilsanalyse. Um mehr über die Forschungsmethodik zu erfahren, senden Sie eine Anfrage an unsere Branchenexperten.

Anpassung möglich

Data Bridge Market Research ist ein führendes Unternehmen in der fortgeschrittenen formativen Forschung. Wir sind stolz darauf, unseren bestehenden und neuen Kunden Daten und Analysen zu bieten, die zu ihren Zielen passen. Der Bericht kann angepasst werden, um Preistrendanalysen von Zielmarken, Marktverständnis für zusätzliche Länder (fordern Sie die Länderliste an), Daten zu klinischen Studienergebnissen, Literaturübersicht, Analysen des Marktes für aufgearbeitete Produkte und Produktbasis einzuschließen. Marktanalysen von Zielkonkurrenten können von technologiebasierten Analysen bis hin zu Marktportfoliostrategien analysiert werden. Wir können so viele Wettbewerber hinzufügen, wie Sie Daten in dem von Ihnen gewünschten Format und Datenstil benötigen. Unser Analystenteam kann Ihnen auch Daten in groben Excel-Rohdateien und Pivot-Tabellen (Fact Book) bereitstellen oder Sie bei der Erstellung von Präsentationen aus den im Bericht verfügbaren Datensätzen unterstützen.